Quando AMD si mise a studiare l'erede del processore K6, in quel di Sunnyvale giunsero diversi ingegneri provenienti direttamente da DEC, l'azienda produttrice dei fantastici processori Alpha. A guidare questo piccolo gruppo di ingegneri c'erano Dirk Meyer e Jim Keller. Correva l'anno 1996.

Jerry Sanders, CEO di AMD, nel biennio 1995-1996 decise di smettere di rincorrere Intel: avrebbe voluto superarla tecnologicamente. Per far questo spinse sull'acceleratore sia nello sviluppo di nuovi processi produttivi (giunse ai 180nm prima di Intel, e con un nodo migliore), ma soprattutto investì nello sviluppo di architetture avveniristiche. Meyer e Keller avrebbero dovuto guidare AMD nello sviluppo di quest'ultime.

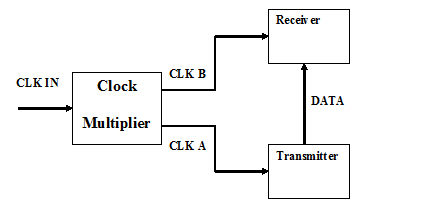

Common Clock

Source Synchronous Clock

Poiché AMD, nei piani di Sanders, si sarebbe dovuta inserire nell'altamente remunerativo settore delle CPU per Server Enterprise, gli ex ingegneri della DEC avrebbero dovuto creare un ecosistema hardware non solo migliore rispetto a quello Intel, ma anche più economico. Una sfida che molti ritenevano impossibile.

Meyer e Keller per sviluppare l'HyperTransport presero come base il Bus EV6, utilizzato come FSB di sistema per l'architettura K7. L'EV6 fu sviluppato da DEC per i propri processori Alpha, ed inizialmente era stato pensato per un impiego prettamente Enterprise. AMD lo portò nel mercato consumer.

Fino a quel tempo le configurazioni multi CPU x86 di Intel utilizzavano un Bus condiviso. Ciò significava che tutte le CPU in un sistema multi socket trasferivano e ricevevano i dati da un unico canale bidirezionale, e che la bandwitdh non sarebbe aumentata all'aumentare del numero di CPU, rimanendo costante. Questo aveva tre difetti, principalmente. Il primo di tipo tecnico. Poiché questo scambio dati era gestito dal chipset, nel caso vi fosse stata la saturazione della banda dati sarebbero aumentate notevolmente le latenze. Lo smistamento dei dati avrebbe portato le CPU a dover interrompere frequentemente il lavoro, in attesa di nuovi dati. Secondo problema, era la bassa bandwidth del Bus GTL+ tra CPU e NorthBridge, pari al massimo a 1066 MB/s nei sistemi Pentium III. In un sistema multi socket era facilmente saturabile, e quindi si sarebbe incontrata spessissimo la situazione descritta al punto uno. Terzo problema, era il costo di disegno delle schede madri. L'implementazione del Bus GTL+ nel PCB delle schede madri era molto costoso. Da un articolo di Anandtech: "Saturation of the 100MHz GTL+ bus happens most frequently in high-end workstations and servers, and is especially easy to point out in multiprocessor systems. The GTL+ bus is a shared bus, meaning that regardless of how many processors you have present in your system, they must all share the same 800MB/s of bandwidth. This is part of the reason that adding more than two processors to an Intel Xeon server begins to give you diminishing returns, and it is also part of the reason that many companies pursue multiple dual processor servers versus a handful of quad processor servers".

Diagramma Bus EV6

Il Bus EV6 limitò in parte questi problemi. Le CPU, in un sistema multi socket, erano collegate singolarmente al North Bridge tramite un canale esclusivo, ed ogni canale aveva una Bandwidth teorica pari a 1.6 GB/s (con Bus a 200 MHz). Questo permetteva alle CPU di comunicare in maniera esclusiva con il NB, evitando eventuali colli di bottiglia, ed al contempo abbassando notevolmente le latenze. La comunicazione tra NB e periferiche, per il momento, sarebbe avvenuta ancora attraverso il Bus PCI (AGP, nel caso delle GPU).

Specificità del BUS EV6 è la presenza di un Bus bidirezionale a 72 Bit, dove i dati in uscita ed i dati in entrata viaggiano su due canali fisicamente distinti, mentre la frequenza, limitata tra i 200 MHz e i 400 MHz (con una banda compresa tra gli 1.6 e 3.2 GB/s), consente la realizzazione di schede madri meno costose rispetto a quelle tradizionali. Il trasferimento del clock, inoltre, avviene contemporaneamente allo scambio dati (Source Synchronous Clock), diminuendo così le latenze ed aumentando l'efficienza: la lettura e la scrittura dei dati avvengono contemporaneamente. Il Bus utilizzato da Intel (prima il GTL+, poi l'AGTL+/QuadPumped) era invece basato sul sistema Common Clock: i dati vengono inviati a tutti i dispositivi, ed ognuno li elabora quando ne ha possibilità, aumentando così i problemi relativi alla latenza.

Negli anni seguenti Intel, per mitigare questo svantaggio, aumentò notevolmente la frequenza del Quad Pumped Bus durante l'evoluzione dei Pentium 4, raggiungendo infine gli 800 MHz (200MHz x4), così da aumentare la frequenza cui i dati venivano letti o scritti. AMD, al contrario, poté competere con un Bus di soli 400 MHz (200 MHz x2). Anche per questo le schede madri Socket A costavano meno di quelle Socket 478: il PCB era di più facile disegno e produzione.

Con il progetto SladgeHammer (K8), che avrebbe dovuto prendere il posto di K7, Meyer e Keller passarono ad uno step successivo. Legare con un Bus di tipo Source Synchronous Clock tutte le periferiche. Questo avrebbe permesso di realizzare sistemi multi CPU ancora più efficienti ed economici.