Gli errori del Socket 423

Con il Pentium 4 Intel si apprestava a presentare la prima vera nuova architettura dopo l'introduzione del Pentium Pro nel 1995. Questa nuova architettura prese il nome di NetBurst, e le sue principali caratteristiche erano un numero elevato di stadi di pipeline (20 nel core Willamette, fino a 31 nel core Prescott: per fare un confronto, il Pentium 3 aveva solo 10 stadi di pipeline), così da elaborare, almeno teoricamente, un maggior numero di operazioni per ciclo di clock, l'introduzione delle tecnologie Rapid Execution Engine e Execution Trace Cache, e del Quad Pumped Bus.

La prima volta che Intel parlò approfonditamente della nuova architettura fu all'IDF primaverile del 2000, in febbraio, ma stranamente durante quell'incontro non fu mostrato nulla di funzionante o, comunque, un qualche benchmark. Evidentemente le prestazioni non erano pari alle aspettative. Nell'aprile del 1999, presentando la nuova archiettura agli OEM, Intel parlò di una frequenza di lancio di 1,1 GHz, aspettandosi da AMD una frequenza, per i suoi processori nel medesimo periodo, di 666 MHz: che sorpresa fu per Intel quando AMD agli inizi del 2000 commercializzò la prima CPU a 1GHz!

Per tale motivo Intel cercò di commercializzare il Pentium 4 alla frequenza più alta possibile, anche a scapito dei consumi.

Il numero elevato di modifiche rispetto al Pentium III ha portato alla realizzazione di un'architettura del tutto diversa da quelle conosciute precedentemente, con tutti i pro e i contro del caso. L'alto numero di Pipeline favoriva l'aumento della frequenza della CPU, ma al contempo faceva diminuire l'IPC del processore. Aumentare il numero di operazioni eseguibili per ciclo di clock permette teoricamente di velocizzare l'esecuzione di un'applicazione, ma allo stesso tempo richiede di ricominciare da capo (svuotamento e riempimento della Pipeline) nel caso in cui un'operazione tra il primo ed il penultimo stadio fosse sbagliata.

Detto più semplicemente, attraverso un'analogia, in un compito in classe di matematica possiamo fare i conti con la calcolatrice e segnarli di volta in volta su un foglio o farli a mente e cercare di ricordarli quando servono. Il primo caso è l'architettura PIII di Intel o Athlon/Duron di AMD, il secondo il NetBurst.

Nasce così l'esigenza di sviluppare tutta una serie di tecnologie capaci di limitare questo importante difetto. La prima era il Rapid Execution Engine, capace di far operare al doppio della frequenza di clock le ALU del processore. La seconda era la Execution Trace Cache, impiegata per memorizzare micro codice che verrà ripetuto più volte. La terza, e più famosa, è il Quad Pumped Bus, bus di sistema tra CPU e Northbridge che quadruplicava l'ampiezza di banda.

Allo stesso modo, per coadiuvare queste caratteristiche, Intel adottò le nuove, velocissime (rispetto alle Sdram), ma anche costosissime memorie, prodotte da Rambus, RDRAM. Attraverso queste caratteristiche gli ingegneri Intel si aspettavano di raggiungere la frequenza di 10 GHz nell'arco di alcuni anni ma, come vedremo in seguito, le loro speranze furono fiaccate da diversi problemi.

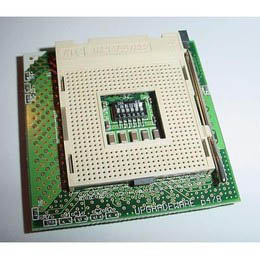

Adattatore per utilizzare processori Socket 478 su schede madri Socket 423